board level drop test reliability of ic packages|micromachine board level drop test : solutions This paper discusses the effect of board design, the failure mechanism and the board level drop impact performance of two types of common IC packages for hand held electronic product applications namely QFN and CSP, when subjected to the JESD22-B111 . WEB爱词霸权威在线词典,为您提供taken的中文意思,taken的用法讲解,taken的读音,taken的同义词,taken的反义词,taken的例句等英语服务。

{plog:ftitle_list}

Written bySteven Hubbard. Verified byBettingLounge team. Last updated31/01/2024. Short Answer. Betfair's Acca Edge replaced the Acca Insurance a few years back and is a .

This paper discusses the effect of board design, the failure mechanism and the board level drop impact performance of two types of common IC packages for hand held electronic product applications namely QFN and CSP, when subjected to the JESD22-B111 .Abstract: Board level reliability during drop impact is a major concern for electronic . This paper discusses the effect of board design, the failure mechanism and the board level drop impact performance of two types of common IC packages for hand held electronic product. This paper discusses the effect of board design, the failure mechanism and the board level drop impact performance of two types of common IC packages for hand held .

Abstract: Board level reliability during drop impact is a major concern for electronic packages. The impact force generated as the casing strikes the ground can cause . In this work, the dynamic response characteristics of electronic packages when subjected to board level drop impacts are investigated. Initially, board level drop tests are .

Reliability performance of IC packages during drop impact is critical, especially for handheld electronic products. Currently, there is no model that provides good correlation with . In this paper, reliability performances of board-level chip-scale packages subjected to four JEDEC drop test conditions were evaluated experimentally and numerically. .

micromachine board level drop test

This paper aims to discuss the effect of board design, the failure mechanism and the board level drop impact performance of two types of common IC packages for hand held electronic product,. Abstract: This paper discusses the effect of board design, the failure mechanism and the board level drop impact performance of two types of common IC packages for hand . A simple, easy-to-use and physically meaningful predictive analytical (mathematical) stress model is suggested for the evaluation of the dynamic response of a PCB .

In this study, reliability performances of board-level chip-scale packages subjected to four JEDEC drop test conditions: A (500 G; 1.0 ms), B (1500 G; 0.5 ms), F (900 G; 0.7 ms), and H (2900 G; 0.3 ms) were evaluated experimentally and numerically. For each of the test conditions, over 80% of the failed solder joints fractured on the package side.

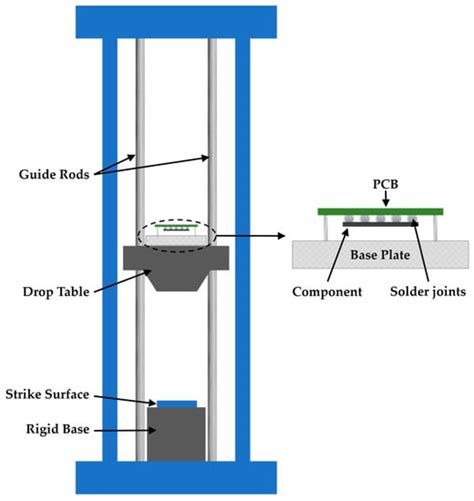

Reliability performance of IC packages during drop impact is critical, especially for handheld electronic products. Currently, there is no model that provides good correlation with experimental measurements of acceleration and impact life. . Board level drop test can be better controlled, compared with system or product level test such as .Unlike component-level reliability testing with BLR, the distinctive requirement is that the component is surface mounted to the test board/interposer, ideally emulating thermo-mechanical stresses that the component would be exposed in the application. (The test board design, construction and materials are selected with this goal.) As shown in Fig. 2, the board-level test vehicle is mounted on the base plate with the corners fixed on the standoffs while the base plate is welded to the drop table.Ideally, the standoffs should move synchronously during the drop impact process. Defined by JEDEC [34], [35], an accelerometer is attached to the base plate at a specific location to monitor peak . For various electronics packages such as IC and area array packages (BGA, CSP etc.), the reliability of the solder joint during thermal cycling test is a critical issue.

of the board-level reliability of such large, ultrathin glass ball grid array (BGA) packages directly mounted onto a system board, considering both their thermal cycling and drop-test performances. To investigate board-level reliability, glass BGA packages, 18.5 × 18.5 mm2 in body size and 100 µm in thickness, Therefore, under the influence of the acceleration of gravity, the weight of the ball grid array(BGA) package, the number of balls, solder ball material, and the solder ball pad size in the drop test are recognized as important factors affecting the .DOI: 10.1016/j.microrel.2007.03.005 Corpus ID: 19096690; Effects of different drop test conditions on board-level reliability of chip-scale packages @article{Lai2008EffectsOD, title={Effects of different drop test conditions on board-level reliability of chip-scale packages}, author={Yi-Shao Lai and Po-Chuan Yang and Chang-Lin Yeh}, journal={Microelectron.

Board level drop test: This test is intended to evaluate and compare drop performance of WLCSPs for handheld electronic product applications in an accelerated test environment, where excessive flexure of a circuit board causes product failure. It is particularly applied to the power Mosfet and analog wafer-level chip-scale package. Various literatures have been studied to characterize the drop impact model of the printed circuit board used in drop test analysis. Lai et al. [5] investigated board level drop reliability of electronic packaging assemblies subjected to drop testing scenario.The drop testing was carried out with pulse-controlled service condition B specified by the JEDEC standard. Reliability performance of IC packages during drop impact is critical, especially for handheld electronic products. Currently, there is no model that provides good correlation with experimental measurements of acceleration and impact life. . –Cu or Sn–Pb solder joint compositions, fluxes, and substrate pads with Ni/Au surface finish or .

This paper describes the first demonstration of the board-level reliability of such large, ultrathin glass ball grid array (BGA) packages directly mounted onto a system board, considering both their thermal cycling and drop-test performances. To investigate board-level reliability, glass BGA packages,

unconfined compressive strength test machine

Resultado da 24 de jan. de 2024 · DLP® technology by Texas Instruments in cooperation with ViALUX offers a good base for latest product innovation.

board level drop test reliability of ic packages|micromachine board level drop test